Infineon Applied sciences final week launched the automotive trade’s first LPDDR Flash reminiscence to assist the event of latest E/E (electrical and digital) programs for semi-autonomous autos. Protected, reliable, and real-time code execution, which is crucial for automotive zone and area management, is supplied by the Infineon SEMPER X1 LPDDR Flash resolution.

In keeping with Infineon, the system permits 20 instances faster random learn transactions for real-time purposes and performs eight instances higher than standard NOR Flash reminiscence. Characterizing one of these efficiency enchancment as outstanding is just not hyperbolic.

Typical NOR Flash reminiscence is usually referred to as non-volatile storage, that means that storage units with that kind of flash reminiscence retain the info with out utilizing a battery or different powered voltage provide. This functionality has made it attainable for software-dependent automobiles to supply cutting-edge options with improved safety and architectural flexibility.

Subsequent-Gen Automobiles Are Computer systems on Wheels

As I’ve noticed in earlier columns, fashionable automobiles have developed into computer systems on wheels over the previous 20 years. Subsequent-generation automobiles rely upon cutting-edge multicore computer systems created utilizing fashionable manufacturing strategies.

As a result of intelligence and real-time connectivity are wanted to fulfill the necessity for security and dependability in autonomous driving eventualities, higher-density built-in non-volatile reminiscences are not a financially viable various. Nevertheless, these refined automotive real-time computer systems require extra extraordinary efficiency than is obtainable in present reminiscence options.

Infineon created SEMPER X1 with a confirmed LPDDR4 interface operating at 3.2 GB/second and a multi-bank structure to handle area and zone controller efficiency and density wants.

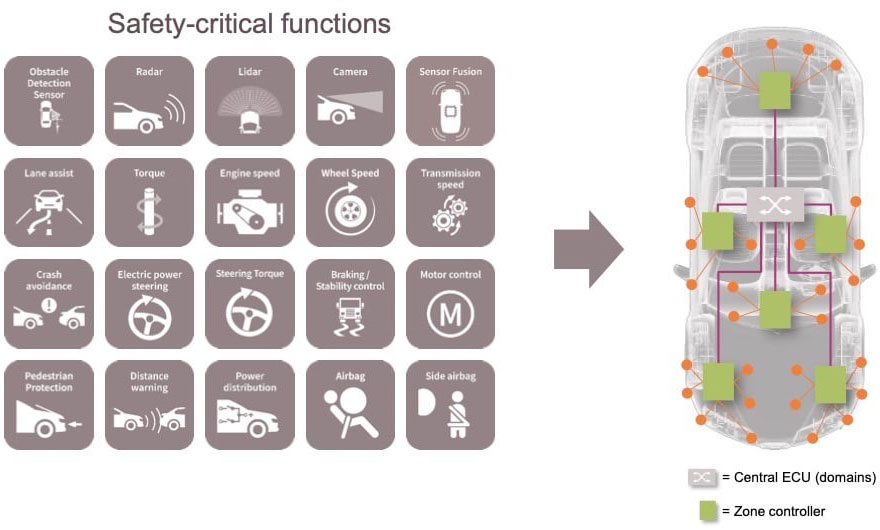

Conventional safety-critical features in a next-gen automotive (Supply: Infineon Applied sciences)

The ensuing worth proposition is sort of compelling. Infineon {couples} flash reminiscence with an LPDDR (Low Energy Double Date Charge) interface to permit extra dramatic efficiency and scalability than xSPI NOR flash to fulfill the brand new necessities of automotive zone designs. The selection by Infineon to make the most of this interface is sensible, on condition that the interface has been available on the market for years and has a low-risk implementation fame.

From a automobile standpoint, the transition to software-defined automobile architectures has prompted a reminiscence problem for next-generation auto designs. Conventional xSPI NOR Flash reminiscence is insufficient for a number of causes, value being a major one. SEMPER XI leverages the LPDDR interface methodology from the DRAM trade to handle new computing necessities within the vehicle trade.

Key Automotive Asks: Rising Efficiency, Density Calls for

Subsequent-generation semi-autonomous cars more and more require extra flash reminiscence and faster efficiency. Automobiles have been transferring towards zonal designs with no-compromise real-time processing for a while. These calls for for greater efficiency merely can’t be glad by what strange NOR flash storage offers as we speak.

The rising variety of area and zone controllers showing in next-gen semi-autonomous autos should course of huge volumes of information in actual time whereas consolidating quite a few safety-critical operations.

These zone controllers have intense real-time computing wants. Whereas these controllers ship info to the principle ECU (Digital Management Unit), these zonal controllers should additionally handle steering, engine, and different essential security features.

Automotive zone controllers are consistently being pushed to supply better efficiency ranges to satisfy these real-time processing necessities. A controller with built-in embedded reminiscence on board merely can’t deal with this heightened stage of advanced processing.

Faster Entry to Exterior Flash Wanted

The processing necessities of next-generation vehicle designs have induced a shift away from real-time processors with few CPU cores and onboard flash. At a excessive stage, one can fairly state that the evolution of semiconductor know-how has prompted a mismatch between the CPU and reminiscence.

Given the fee strain within the smart car and EV markets, including onboard flash isn’t economically viable using as we speak’s superior semiconductor course of nodes employed by these processor options.

The fact is that quick, real-time multicore processors, which function from exterior flash reminiscence, are mandatory to fulfill the necessities of next-generation automotive designs.

Automotive-qualified embedded flash applied sciences have difficulties with excessive value (giant die areas) and lack of scalability at superior manufacturing nodes. As well as, the trade requires further flash reminiscence to accommodate the increasing code dimension and complexity.

xSPI Is Unscalable and Runs Out of Fuel

All these components seem to have influenced Infineon’s function in creating LPDDR Flash reminiscence.

Infineon VP of Advertising and Purposes, Sandeep Krishnegowda, has been clear that the corporate utilized high-profile OEM suggestions to assist outline the LPDDR reminiscence class as the best resolution to handle the rising want for real-time compute functionality for code execution by multicore processors. This strategy is sensible as quick random entry is on the coronary heart of LPDDR flash.

Undoubtedly, this methodology accelerates execution charges. In keeping with Infineon, when in comparison with a typical Octal (x8) xSPI NOR flash chip, utilizing LPDDR flash offers a shocking 20x enhance in efficiency. Conversely, this efficiency enchancment is required to toggle from the real-time computations contained in the CPU to these in exterior reminiscence.

With its LPDDR interface, the SEMPER X1 flash can ship throughput charges of as much as 3.2 GB/second. Its multi-bank design permits over-the-air firmware adjustments with no downtime, which is essential in autonomous driving eventualities. The system additionally consists of enhanced error correction and different security measures, and it complies with ISO 26262 ASIL-B.

Different components come into play driving the substitute of xSPI with LPDDR flash.

First, xSPI, as a legacy interface, is just not solely too sluggish however doesn’t scale adequately from a future wants standpoint. This essential issue can be driving demand for LPDDR flash. Additional, xSPI units available on the market as we speak use a low voltage complementary steel oxide semiconductor (LVCMOS) strategy that may’t scale past 200MHz, prompting the necessity for an answer with greater bandwidth.

Provided that context, standard Octal xSPI flash units are unsuitable for code execution as a result of they can not accommodate as we speak’s gigahertz multicore processors.

Closing Ideas

Infineon’s SEMPER X1 is a vital step in that path because it facilitates extra advanced engine management and real-time decision-making bolstered by a reminiscence structure that may develop independently of the CPU.

This new non-volatile reminiscence class shall be fascinating to observe because the ecosystem grows. My latest podcast with Krishnagowda offers some intriguing perception into what he believes are the disruptive implications of this new announcement.

Infineon has been a bit cagey about market classes past the auto area that LPDDR Flash reminiscence may enchantment to.

Linus Wong, Infineon’s Director of Product Administration for SEMPER X1, acknowledges that warehousing, safety, and medical purposes might even see great curiosity on this new storage functionality. “After we have a look at these secondary markets, it actually comes all the way down to the improved worth proposition for [usage models] that may exploit latency enhancements measured within the 1000’s of a second,” he mentioned.

Lastly, it’s not insignificant that Infineon has taken an trade management function in releasing this new reminiscence resolution. The corporate’s gravitas, long-time fame for design-in excellence, and historical past of stable execution that’s essential with excessive ASP next-gen autos are all tailwinds that favorably assist market acceptance of LPDDR Flash reminiscence.

In keeping with Infineon, SEMPER X1 is now present process sampling, with a industrial launch scheduled for a while in 2024.

Discussion about this post